### **Context**

- From March May 2013, I did the first-ever MOOC on how we build EDA tools for chip design, on Coursera

- In contrast to lots of MOOCS, explicitly a "grad level" course

COURSER | Global Partners | Courses Partners | About | Sign In | Sign Up

### **VLSI CAD: Logic to Layout**

Rob A. Rutenbar

A modern VLSI chip has a zillion parts -- logic, control, memory, interconnect, etc. How do we design these complex chips? Answer: CAD software tools. Learn how to build these tools in this class.

Workload: 10-12 hours/week

Taught In: English

Subtitles Available In: English

### **More Context**

- I spent 25 years on faculty in ECE at Carnegie Mellon

- And I taught this class...

- About 15 times over the years

- To about 700-750 students over these years

- Class called: VLSI CAD: Logic to Layout

- I "came of age" in Mead&Conway era, so it's "VLSI" and "CAD" for me...

- ...even tho in course I explained "yeah, it's really EDA"

## What Does the "Regular" Class Teach?

### Classical ASIC Flow

- Some models

- Some synthesis

- Some verification

- Some logic, some layout

- Some timing

Logic Synthesis

Logic Verification

Layout Synthesis

Timing Verification

### Topics

- Computational Boolean Alg

- Logic verification: BDDs, SAT

- FSM verification (no model check)

- Logic synthesis: 2-level, multi-level

- Technology mapping

- Timing analysis: static + electrical

- Placement (Iterative, mincut, analytical)

- Routing: maze

- Geometric data structures

- Extras: eg, Litho simulation

## Physical On-Campus Class -> MOOC

- My physical class is

- 15 weeks

- 948 PPT slides

- 20 separate slide decks

- Delivered as roughly 14\*3 hours (est) = 52 hours of lecs

- But, typical MOOC not same length & intensity as a standard semester

- F09 Lec 00 INTRO.annote.pdf F09 Lec 01 ADV BOOL1.annote.pdf F09 Lec 02 ADV BOOL2.annote.pdf F09 Lec 03 BDD1.annote.PDF F09 Lec 04 BDD2.annote.PDF F09 Lec 05 FSMVERIF.annote.PDF F09 Lec 06 SAT1 .annote.PDF F09 Lec 07 SAT2 .annote.PDF F09 Lec 08 2LEVELSYN 2.annote.PDF F09 Lec 09 MULTILEVEL 1 MODEL.annote.PDF F09 Lec 10 MULTILEVEL 2 EXTRACT.annote.PDF F09 Lec 11 MULTILEVEL 3 DONT CARES.annote.PDF F09 Lec 12 TECHMAP.annote.PDF F09 Lec 13 PLACE1.annote.PDF F09 Lec 14 PLACE2.annote-BT.PDF F09 Lec 16 Route.annote-BT.PDF F09 Lec 17 Placer3.annote.PDF F09 Lec 18 Static Tlming.annote.PDF F09 Lec 19 Elmore Delay.annote.PDF xF05 Lec xx PROJ1 FSM EQV SAT v01.ppt.pdf

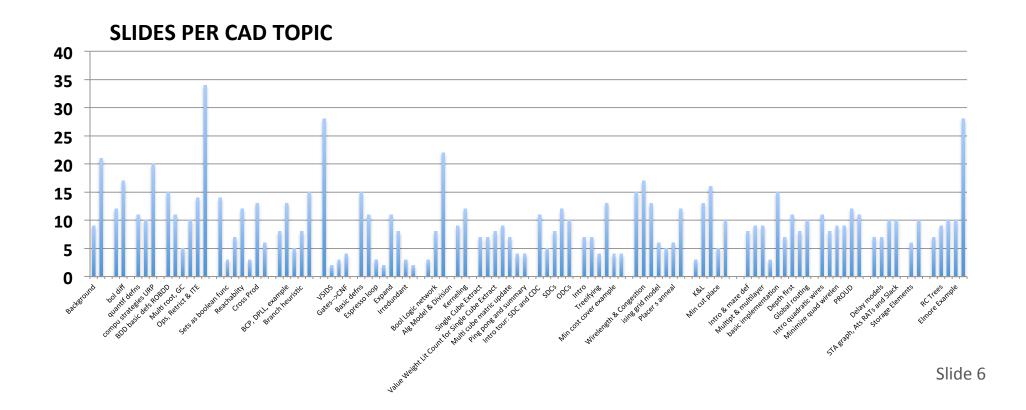

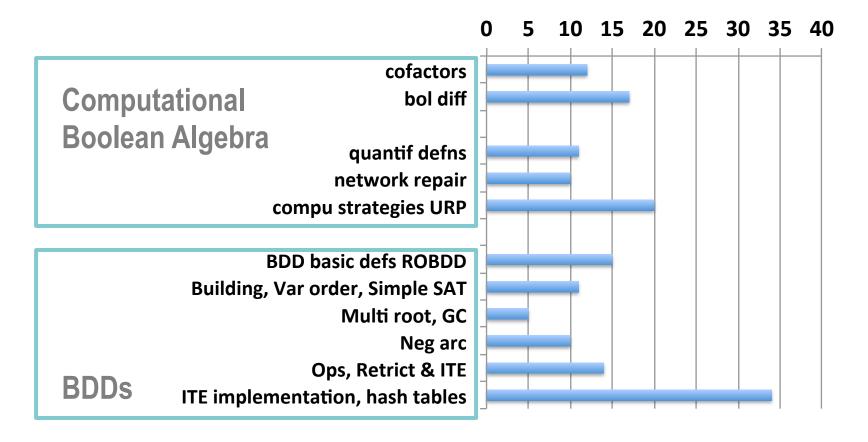

## **Designing Coverage for my MOOC**

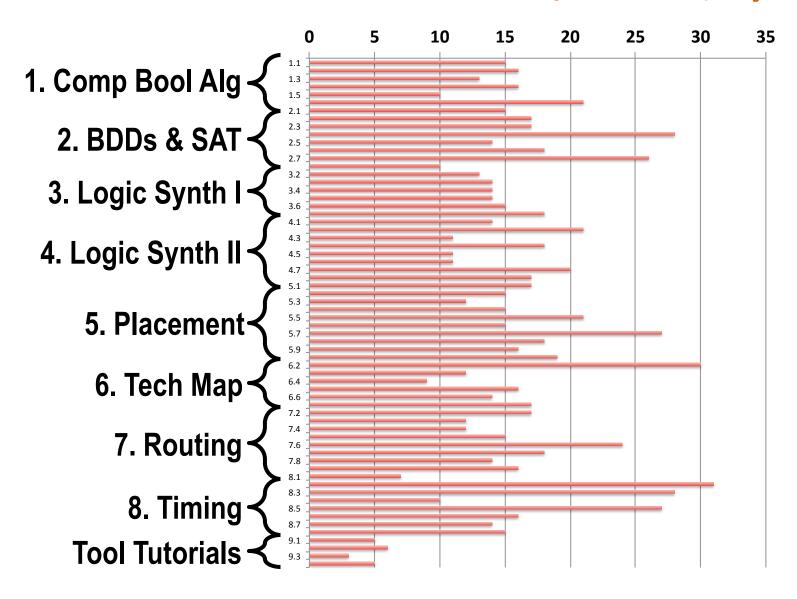

- Walking thru each lec slide by slide, and chunking into individual essential topics, was for me a very useful exercise

- I have ~102 separate topics, with per-topic slides counts below

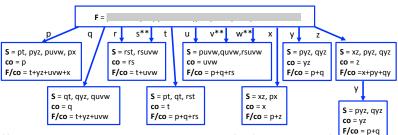

## **Closeup on Topical Coverage**

Example of 2 topics, up close, PPT lecture slide counts

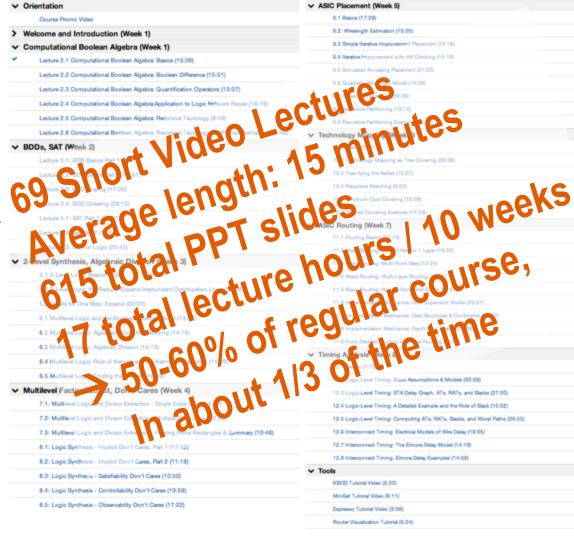

## **Result: From Regular Course to MOOC**

Regular class: 20 Lectures 948 PPT slides

### **MOOC Video Content: Minutes/Lecture, by Week**

## Why Many Short Video Segments?

### Pedagogy

- Better retention with short bursts of focused instruction

- Emphasize one (or few) core topics

### Bandwidth

- In much of planet, cannot download 2-hour video as 1 chunk

- So- keep vids short. Don't stream "live". Download, view later

- Critical to respect infrastructure realities for successful MOOC

### What's In A Video Lecture?

Start with "talking Rob head" intro of lecture topic

### What's In A Video Lecture?

Most content is me writing-on-the-slides of lec + voiceover

### **MOOC** Assignments

- 8 weekly homeworks, aka, Problem Sets

- True/False

- Multiple Choice

- Type a number in a box, etc

- What's different than in-class versions?

- Can't do math derivations

- Must "over supply" sub-problems, and randomize (cheating)

- Partition big problems into smaller, step-by-step parts

- Took about 3 HW sets to "get this right", style-wise

### **Example: One HW Problem Spec**

### Q1 Single-cube extraction from multi-level logic. Consider this Boolean logic network with variables a,b,c,d,e,f: 5 R = abf + abcd + abce + cdf S = acd + cdef + abce 7 T = cdef + af Build the cube-literal matrix associated with this set of functions. Look at what prime rectangles are possible in this matrix. Which are the following are correct statements about extractions using this matrix? 5 OPTION GROUP 1: SELECT 2 randomize (These are all correct statements) § Single cube divisor an be extracted as a prime rectangle. It has 2 columns and 4 rows Extracting this divisor saves 3 literals. • - Single cube divisor are can be extracted as a prime rectangle. It has 2 columns and 3 rows ( Extracting this divisor saves 2 Single cube divisor are can be extracted as a prime rectangle. It has 3 columns, and 2 rows Extracting this divisor saves 3 literals. Single cube divisor a an be extracted as a prime rectangle. It has 2 columns and 2 rows ( Extracting this divisor saves 0 literals - i.e. no fewer literals in this new factored network. 5 OPTION GROUP 2: SELECT 1 randomize (These are all correct statements) § This is a correct extraction associated with a prime rectangle in this matrix. This is a correct extraction associated with a prime rectangle in this matrix. This is a correct extraction associated with a prime rectangle in this matrix.

Randomize selection from this 1<sup>st</sup> group of sub-questions

Randomize selection from this 2<sup>nd</sup> group of sub-questions

Etc...

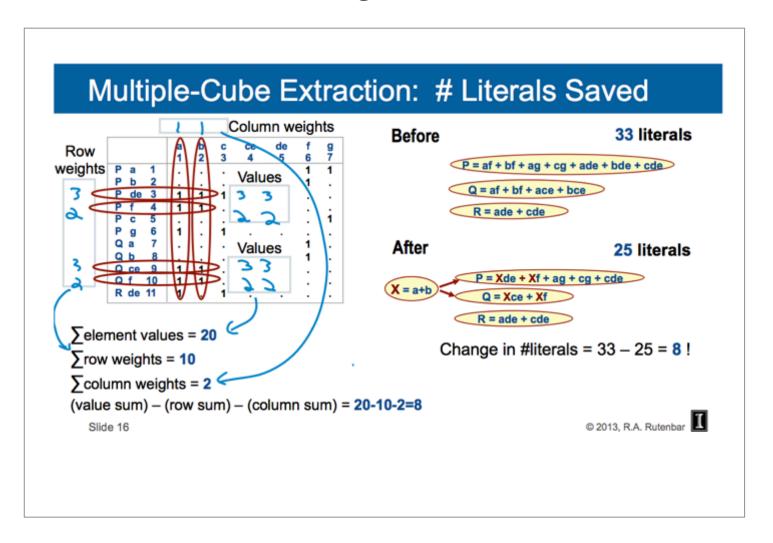

## **MOOC Assignments**

- Lots of criticism of MOOCs being "dumbed down"

- Yes, they are a bit simpler. No, not a lot "dumber"

- Mostly, burden on instructor to design smart assignments

- Ex: this is the "macro answer" to one factoring HW problem

### **MOOC Assignments: 2 Paths Thru Class**

### Grading: Certificate & 2 Badge Options

Two options for a Statement of Accomplishment Certificate

- Achievement Badge

- 8 Problem Sets = 75%

- L'A

- Single submission; late submission allowed after deadline for 50% of credit

- 1 Final exam = 25%

- Single submission.

- Idea: Do this is you don't have time to do all the code

- Mastery Badge

- 8 Problem Sets = 40%

- Same single submit policy

- 4 Program Assignments = 40%

- Multiple submissions ok; late submission allowed after deadline for 50% of credit

- 1 Final exam = 20%

- Same single submission

- Idea: Do this for deepest understanding of course

Slide 4 © 2013, R.A. Rutenbar

### **EDA MOOC: Some Philosophy**

- I don't believe you can teach a serious EDA course without:

- Experimenting with some existing EDA tools

- Designing software to build some EDA tools

- How to do this at scale? To 10,000 students?

- CDNS, SNPS, etc, are not going to give us free stuff

- Lots of IP, Licensing, etc, landmines: you get to know your university's top lawyers on a first name basis, in your MOOC

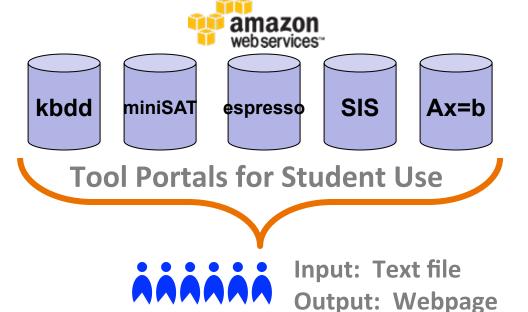

### Answers

- Carefully select open source software

- Write everything else yourself

### **VLSI CAD MOOC: Software Ecosystem**

## Aside: Building this Software Ecosystem

### **VLSI CAD MOOC: Software Ecosystem**

<del>J</del>lide 20

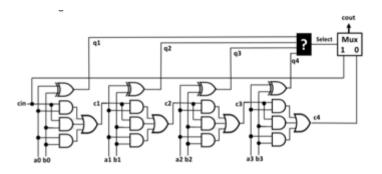

## **VLSI CAD MOOC: 4 Software Projects**

- Boolean Data Structures

Computation (URP,PCN)

- b 11 01 11 c 11 11 01 fab'

fab

fab

fab

c 11 11 11 01 c 11 11 01 c' 11 11 10

- 3. Quadratic Placement

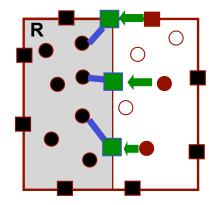

# 2. BDD-based Logic Network Repair

### 4. Maze Routing

| 3       | 2  | 3   | 4 | 5 | 6 |  |  |

|---------|----|-----|---|---|---|--|--|

| 2       | S1 | 2   | 3 | 4 | 5 |  |  |

| 3       | 2  | 3   |   | 5 | 6 |  |  |

| 4       | 3  | 4 v |   | 6 | 7 |  |  |

| 5       | 4  | 5   |   | 7 | V |  |  |

| 6       | 5  | 6   | 7 |   |   |  |  |

| Layer 1 |    |     |   |   |   |  |  |

|         | 8 |                |   |     |   |  |

|---------|---|----------------|---|-----|---|--|

| 8       | 7 | 6              | 7 | 8   |   |  |

| 7       | 6 | 5 <sub>V</sub> | 6 | 7   | 8 |  |

| 8       | 7 | 6              | 7 | 8 T | V |  |

|         | 8 | 7              | 8 |     |   |  |

| Layer 2 |   |                |   |     |   |  |

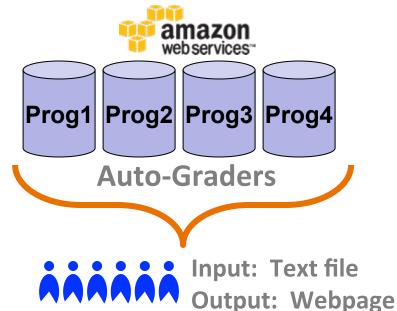

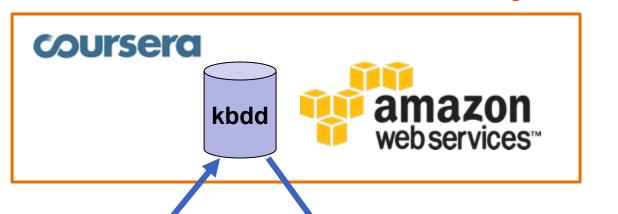

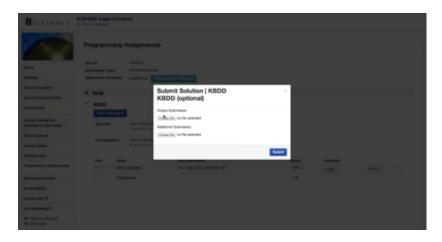

### **About MOOC Software Projects**

- We provide the spec and input data; we grade output file

- Too hard to compile/run other people's code

- Too many platform issues; too many language issues

- ASCII textfile in; ASCII textfile out

- Architect like a real "regression test suite"

- Several benchmarks, from tiny to big

- Partial credit for each part (as much as possible)

- Lots of feedback in the webpage portal about how it went

### **Concrete Example: Regression-Like Benchmarks**

Can you route a 2-point wire in 1 lqyer?? Horizontal?

Vertical? Around obstacle? Straight line? With a bend? etc.

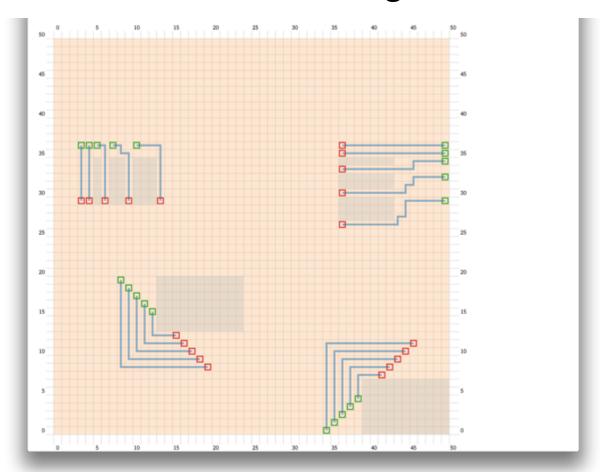

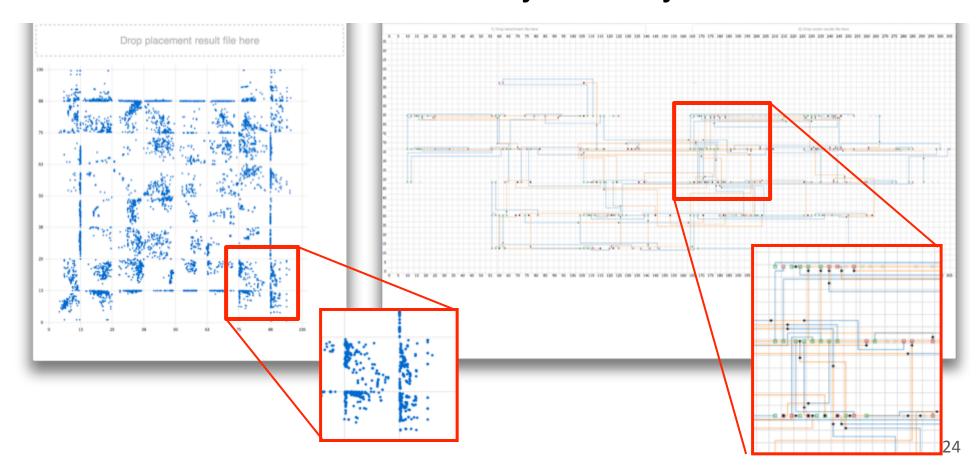

## **Software Project Examples: Layout**

### **Recursive Quadratic Placer**

### 2-Layer ASIC-style Maze Router

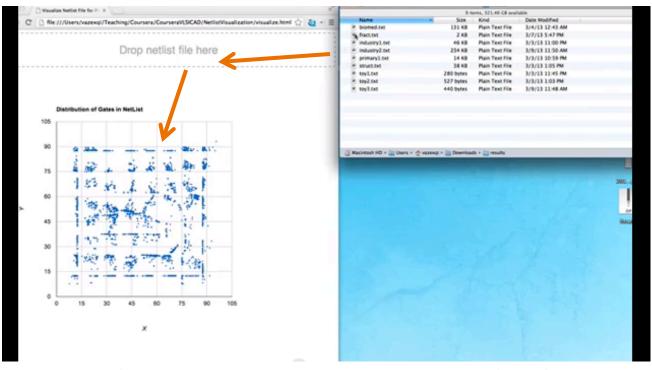

## New Problem: How Can Students See Layout?

- Can't control what platform they use!

- Answer: custom HTML5 geometry web-based environment

- If they have a modern browser, they can drag/drop text file

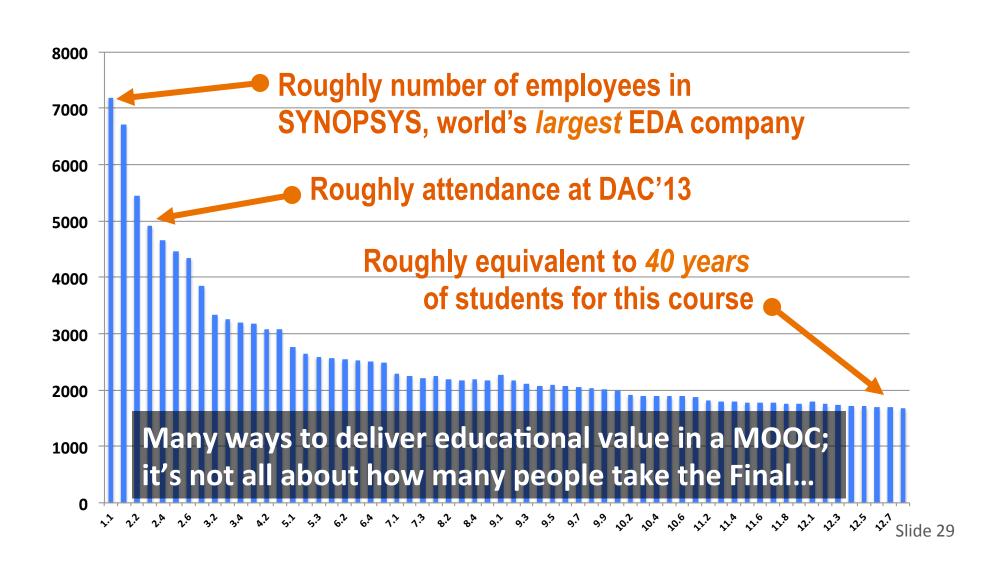

## The Elephant In The (MOOC) Room...

**LOTS** of people start...

**NOT** so many people finish<sub>Slide 26</sub>

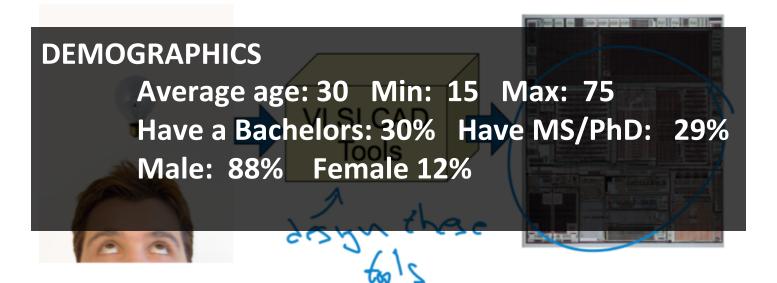

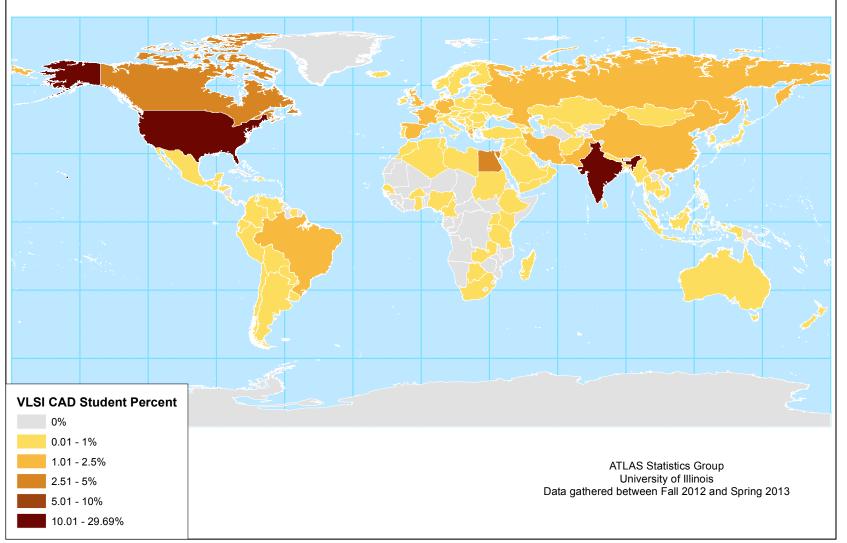

### **VLSI CAD MOOC:** The Participant Landscape

17,500 participants at peak

7,000 people watched a video

1,300 people did a homework

400 people tried a software assignment

500 people took the Final Exam

386 Statement of Accomplishment Cert's

## **Details: Views Across All My MOOC Videos**

## Things One Learns in MOOC-Land...

# My handwriting *unreadable* for a planetary audience

# MOOCers crave *interaction* with instructors, 24x7!

# **Creativity** to make homeworks in multiple-choice format

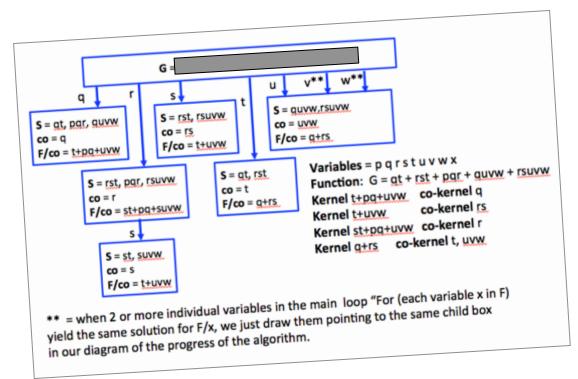

\*\* = when 2 or more individual variables in the main loop "For (each variable x in F yield the same solution for F/x, we just draw them pointing to the same child box in our diagram of the progress of the algorithm.

# Be sensitive to diversity of IT resources of participants

### My MOOCers: Want More EDA...

Word-cloud from **Final Exam question:** what else would you like us to cover

advanced

verification information examples enjoyed problems background problem physical coverage lectures example algorithm tools layout liked work awesome programmir interesting design boolean 'use NiCE just basic covered logic CAD little make know Thanks STA Synthesis delay BDD please detail 1 electrical Thank way first details mapping **PO**( included better algor technology assianments excellent sequential circuits techniques personally optimization understand

## Why Did I Do This...?

Because every vibrant discipline needs a solid on-ramp, and teaching of core-EDA was vanishing, rapidly...

### Reflections...

- If we want to energize a new generation of EDA

- Moving EDA into other areas or kinds of systems

- Moving EDA into new technology platforms (eg, post-Moore)

- Translating EDA "sideways" into adjacent opportunity areas

- If we want to do any of these things, somebody has to be teaching the foundational topics

- Maybe it is the case that planet can only support a handful of these large, global-scale courses on EDA foundations

- Maybe this is only way to reach broadest, global audience

- OK so be it. Here's my shot at "regenerating the excitement"

### Me: Personally Positive on MOOC Potential

coursera

Global Partners

Courses

Specializations New

**Edit Course Description**

Institutions

Edit Session Descriptions▼

About ▼

Rob A. Rutenbar -

Edit Session Materials

I I L L I N O I S

### VLSI CAD: Logic to Layout

A modern VLSI chip has a zillion parts -- logic, control, memory, interconnect, etc. How do we design these complex chips? Answer: CAD software tools. Learn how to build these tools in this class.

Version 002 of my EDA MOOC goes live MARCH 3, 2014

#### About the Course

A modern VLSI chip is a remarkably complex beast: billions of transistors, millions of logic gates deployed for computation and control, big blocks of memory, embedded blocks of pre-designed functions designed by third parties (called "intellectual property" or IP blocks). How do people manage to design these complicated chips?

Sessions

Mar 3rd 2014

Join for Free

## Me: Personally Positive on MOOC Potential

Me, March-May 2013

### **Summary**

- I taught the first-ever EDA MOOC last year

- Exhilarating. Amazing. (Terrifying). Satisfying.

- Why? Because somebody has teach this stuff at scale.

- Why? Because the material is important & beautiful.

- Why? Because need excitement for vibrancy of discipline.

- I'm doing it again this year (in about 2 weeks)

- Ask me at DAC how Round #2 goes....